# Class-B Power MMIC Amplifiers with 70 Percent Power-Added Efficiency

INDER J. BAHL, FELLOW, IEEE, EDWARD L. GRIFFIN, MEMBER, IEEE, ARTHUR E. GEISSBERGER, MEMBER, IEEE, CONSTANTINE ANDRICOS, AND THOMAS F. BRUKIEWA, MEMBER, IEEE

**Abstract** — *C*-band monolithic amplifiers using high-efficiency, class-B MSAG processing have been designed, fabricated, and tested. The class-B single-ended amplifier design employed reactive termination for higher order harmonics and achieved state-of-the art efficiency of 70 percent with associated gain of 8 dB and output power of 1.7 W over the 5–6 GHz band.

## I. INTRODUCTION

HERE IS a great deal of interest in finding efficient, reliable, and low-cost power sources for the T/R modules used in phased array antennas. Many companies have designed high-power MMIC amplifiers in order to meet this challenge. We have developed [1] a single-chip 10 W class-A power MMIC amplifier demonstrating state-of-the-art performance with 5 dB gain and 36 percent power-added efficiency at 5.5 GHz. We also achieved 17 W power out, 4.5 dB gain with 32 percent power-added efficiency, by combining these two chips using external combiners.

However, the need to reduce prime power and cooling requirements for large antenna arrays puts a tremendous premium on achieving significantly higher power-added efficiency. Accordingly, we have investigated class-B amplifiers which have the following potential advantages compared to class A:

- Higher power-added efficiency.

- Negligible power dissipation at no RF power.

- Under backoff, the efficiency of the class-B amplifier does not degrade as rapidly as that of the class-A amplifier.

- A dynamic range of about 10 dB over which the power-added efficiency is greater than 40 percent and the gain is almost constant.

High-efficiency hybrid class-B power amplifiers have been reported in the literature [2]–[9]. Power-added efficiency (*PAE*) of 45 percent with associated gain of 5.4 dB over the 9.2–10.2 GHz band was achieved for a 2 W push–pull power amplifier [5]. For harmonic reaction amplifiers the *PAE* obtained was 75 percent with 2.7 W

output power and 9 dB gain at 1.7 GHz [6], while a 5 W amplifier demonstrated 70 percent *PAE* with 9 dB gain at 2 GHz [7]. An *X*-band power amplifier using a harmonic tuning technique has achieved 5 W of output power with 6 dB gain and 36 percent *PAE* at 10 GHz [8]. A quasi-monolithic 4 GHz power amplifier has demonstrated 65 percent *PAE*, 1 W power output, and 10 dB gain [10].

This paper describes the design, fabrication, and test results of a fully monolithic class-B power amplifier with 70 percent *PAE* at *C*-band. In addition to discussing power output, gain, and *PAE* as a function of input power, drain–source voltage, and gate–source voltage, this paper includes data on noise figure, AM to PM conversion, and second- and third-harmonic generation.

## II. MODELS FOR CLASS-B POWER FET'S

The FET used in our class-B power amplifiers has a 2.5 mm gate periphery. This device employs two plated-through source vias for low-inductance source grounding and good heat sinking. The FET's are biased near pinch-off at a drain–source current of 5 percent  $I_{DSS}$  and a drain–source voltage of 12 V.

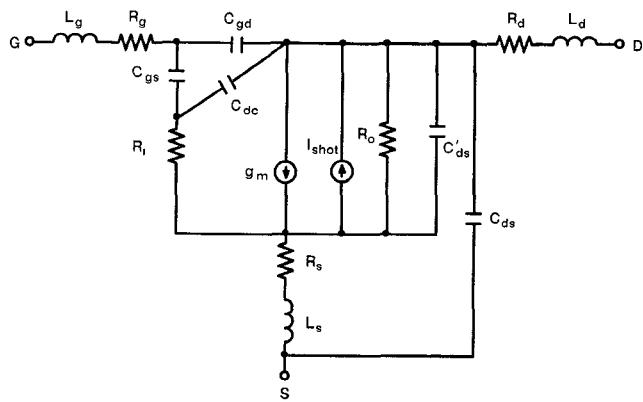

An innovative method has been developed at the ITT Gallium Arsenide Technology Center (GTC) to determine accurate linear-type models for class-B power FET's which are used to design MMIC power amplifiers. A similar technique has been employed successfully at GTC to design class-A power MMIC amplifiers [1]. The model is derived from *I*–*V* characteristics, small-signal *S* parameters measured at 5, 25, and 50 percent of  $I_{DSS}$ , and load-pull contour data at the operating drain–source voltage and frequencies. An equivalent lumped-element model for the 2.5 mm FET biased at  $V_{DS} = 12$  V is shown in Fig. 1. This model is directly used to design matching networks for maximum efficiency of an MMIC amplifier operating in class-B mode.

## III. 1.5 W POWER AMPLIFIER DESIGN

The push–pull configuration has been extensively used for class-B power amplifiers at low frequencies. However, at microwave frequencies low-loss transformers (baluns) for push–pull amplifiers are required to cancel the second harmonic, which is generated when the FET's are biased near pinch-off. Because power MMIC amplifiers must be

Manuscript received January 12, 1989; revised April 13, 1989.

I. J. Bahl, E. L. Griffin, and A. E. Geissberger are with ITT Gallium Arsenide Technology Center, 7670 Enon Drive, Roanoke, VA 24019.

C. Andricos and T. F. Brukiewa are with ITT Gilfillan, 7821 Orion Avenue, Van Nuys, CA 91409.

IEEE Log Number 8929186.

|                    |                            |

|--------------------|----------------------------|

| $R_p = 2 \Omega$   | $C_{gs} = 2.5 \text{ pF}$  |

| $R_l = 0.4 \Omega$ | $C_{pd} = 0.1 \text{ pF}$  |

| $R_s = 0.6 \Omega$ | $C_{dt} = 0.05 \text{ pF}$ |

| $R_d = 0.3 \Omega$ | $C'_{ds} = 0.1 \text{ pF}$ |

| $R_o = 70 \Omega$  | $C_{ds} = 0.1 \text{ pF}$  |

Fig. 1. Lumped-element model for a 2.5 mm class-B power FET.

fabricated on very thin substrates for good thermal dissipation, it is almost impossible to realize these transformers with less than 1 dB insertion loss, since the component loss is inversely proportional to substrate thickness. A transformer with 1 dB loss will lower the *PAE* of a push-pull amplifier by 20 percent. Therefore, the push-pull configuration was not utilized for narrow-band power amplifier designs for our high-efficiency applications. Keeping in mind all the possible limitations, we selected a single-ended class-B amplifier design.

The single-ended class-B amplifier design consists of the reactive termination of higher order harmonics. Two RF bypass capacitor terminated short-circuited stubs ( $\lambda/4$  and  $\lambda/6$  at band center frequency) connected at the drain location reactively short the second and third harmonics to increase the overall efficiency of the circuit [10], [11]. The short-circuited quarter-wavelength stub does not affect the fundamental frequency performance. However, at twice the fundamental frequency, the line becomes  $\lambda/2$  long, providing low impedance to the second harmonic. The short-circuited  $\lambda/6$  stub is inductive at the fundamental frequency and is part of the matching network. At three times the fundamental frequency, this line becomes  $\lambda/2$  and reactively terminates the third-harmonic component.

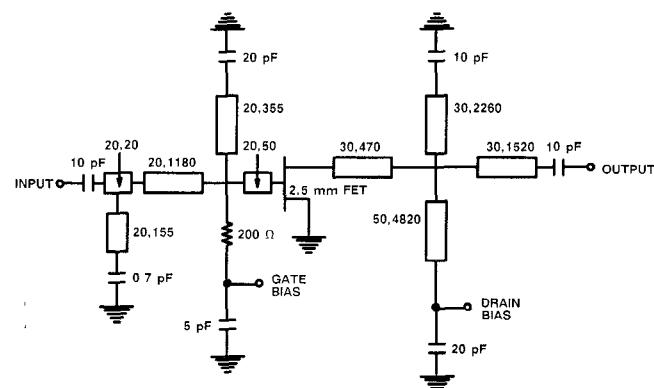

The 1.5 W power class-B MMIC design is based on the design methodology developed at ITT/GTC. The 2.5 mm FET (Fig. 1) for maximum efficiency is matched to 50  $\Omega$  input and output. Both distributed and lumped elements were used in the matching networks. The elements of the output matching network were selected for minimum possible loss with a good match as well as to satisfy electromigration requirements (maximum allowed current density in the bias lines was  $2 \times 10^5$  A/cm<sup>2</sup>). Capacitors, which were used for dc blocking, RF bypassing, and matching, were all of the metal-insulator-metal (MIM) type. The dielectric material used for the capacitors is 2000-Å-thick Si<sub>3</sub>N<sub>4</sub>.

Fig. 2. Schematic of 1.5 W class-B MMIC amplifier. All dimensions in  $\mu\text{m}$ .

This provides a capacitance of 300 pF/mm<sup>2</sup> and a breakdown voltage above 30 V. The tolerance in capacitance is  $\pm 5$  percent. Large RF bypass capacitors as well as resistive gate bias were used for amplifier stabilization at low frequency. The drain bias is applied through a short-circuited stub which is also a part of the output matching network. The amplifier design was optimized over the 5–6 GHz frequency. A schematic of the amplifier is shown in Fig. 2.

#### IV. FABRICATION

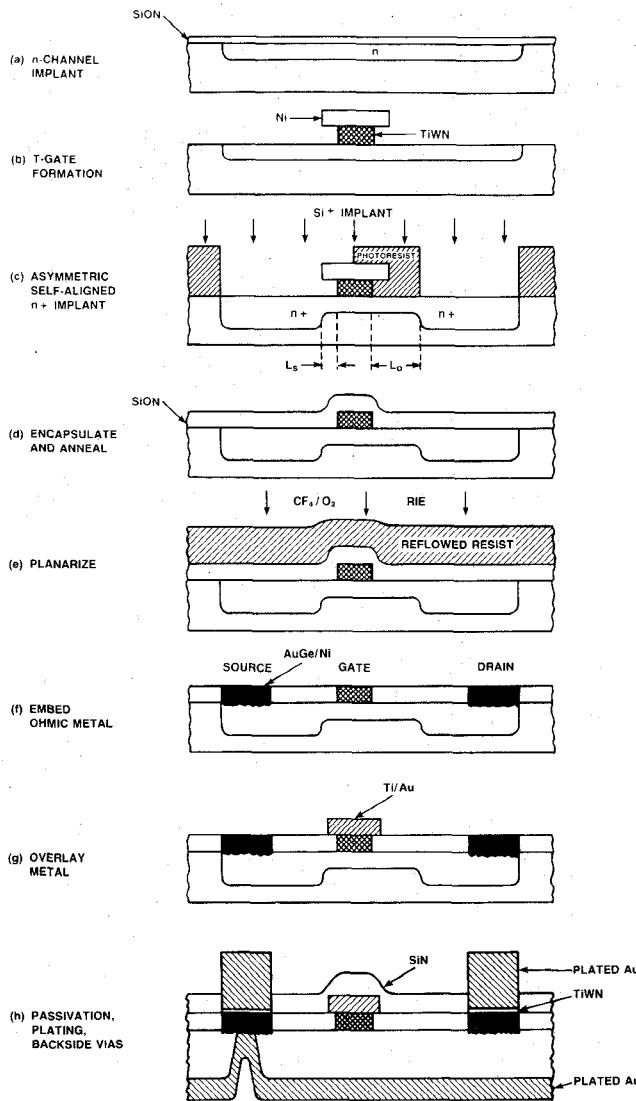

The class-B power IC's reported in this paper are fabricated using the refractory metal, multifunctional self-aligned gate (MSAG) MMIC process developed at ITT/GTC. The process flow diagram is shown in Fig. 3 and a detailed description of the process is given in [12]. Some of the key features of the process are as follows:

- Since the FET  $I_{DSS}$  is determined by implantation rather than gate recess,  $I_{DSS}$  uniformity is remarkably improved. Typical uniformity is better than 5 percent.

- Gate-source resistance is minimized using an  $n^+$  implant which aligns itself to the gate. FET performance is reasonably insensitive to gate location, resulting in excellent photolithography tolerance.

- The Schottky metal is titanium-nitride (TiWN), an extremely good gold diffusion barrier. Given that the Schottky survives an  $825^\circ\text{C}$  anneal, it is unlikely to fail at less than  $300^\circ\text{C}$ .

- The gate parasitic resistance is reduced to a very low level using gold overlay metal which is isolated from the GaAs surface by silicon nitride dielectric and the TiWN Schottky.

- The  $n^+$  on the drain side is moved away from the gate to maintain high gate-drain breakdown voltage and high output resistance.

The devices reported here employ coimplantation of n-type (Si) and p-type (Mg) impurity ions in their active regions. This was done in order to increase the FET transconductance, especially near pinch-off bias, by increasing the abruptness of the charge density profile, and to increase carrier confinement, and hence breakdown

Fig. 3. MSAG FET fabrication process flow diagram.

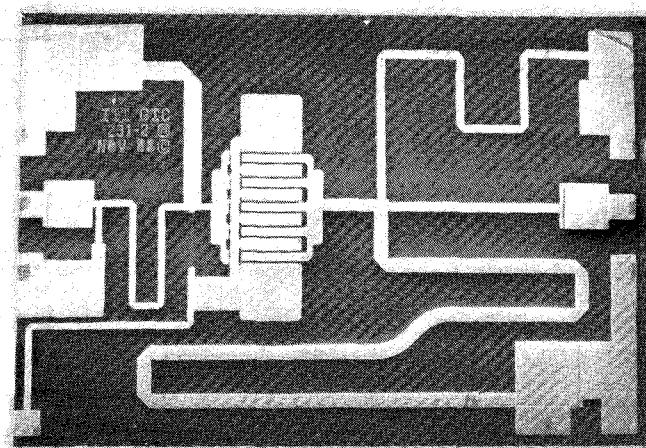

Fig. 4. Photograph of the 1.5 W class-B power MMIC amplifier (chip size = 4.8 mm<sup>2</sup>).

voltage, by generating a p-n junction at the channel-substrate interface.

The process includes Au/Ge/Ni metallization for ohmic contacts, 0.5  $\mu\text{m}$  TiWN Schottky barrier gates, and ion-implanted resistors. The 0.5  $\mu\text{m}$  TiWN gates are covered

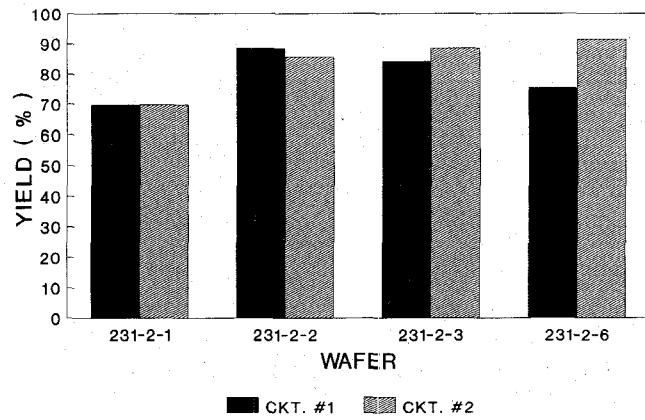

Fig. 5. Functional yield of 1.5 W class-B power MMIC amplifier from a lot of four wafers.

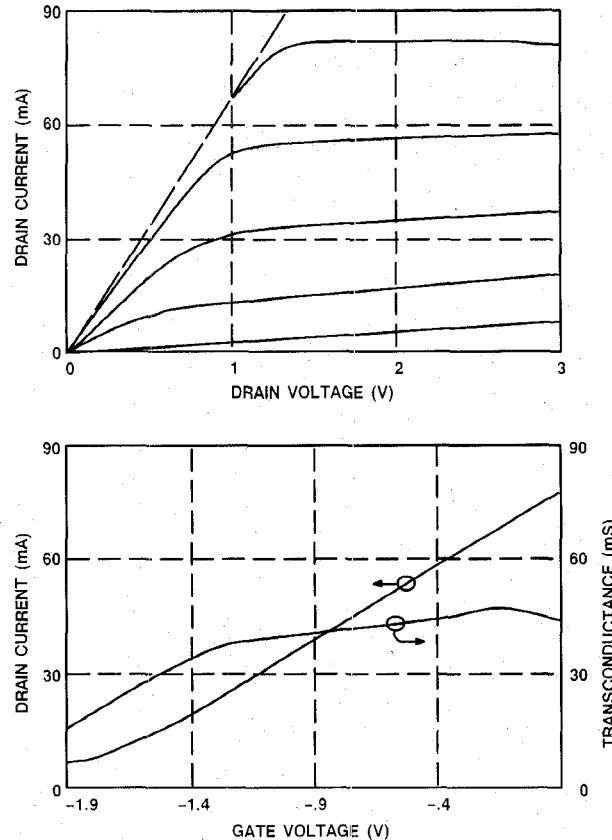

Fig. 6. Typical measured dc data for a 300  $\mu\text{m}$  class-B power FET.

by a 0.8  $\mu\text{m}$  overlay after planarization. Silicon nitride is used for both capacitors and passivation. The air bridges, microstrip lines, and bonding pads are 5- $\mu\text{m}$ -thick plated gold. The wafer is lapped to its final thickness of 75  $\mu\text{m}$ , and back side via holes are then etched and plated. A photograph of the chip is shown in Fig. 4. The measured functional on-wafer yield for four wafers in a lot is plotted in Fig. 5. (This is a low-power screening test.)

## V. TEST RESULTS

Fig. 6 shows the dc characteristics of a 300  $\mu\text{m}$  FET tested on the wafer. The typical  $I_{DSS}$  is 80 mA, and the pinch-off voltage is -2 V. At pinch-off the gate-drain breakdown voltage (defined as  $I_{GD} > 1$  mA/mm) is

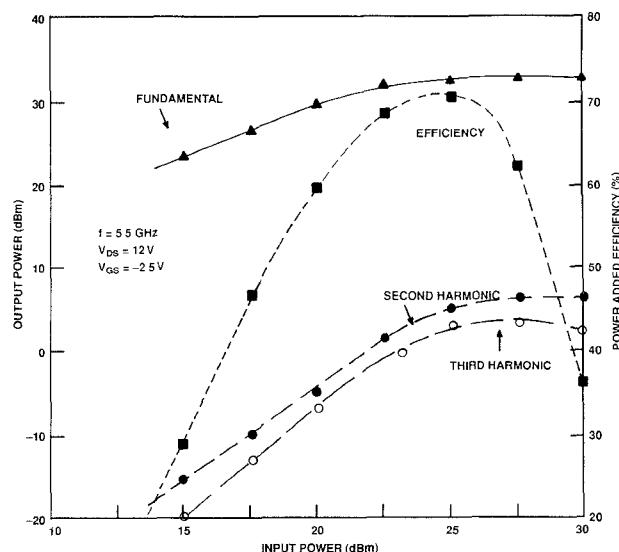

Fig. 7. Output power for fundamental, second and third harmonic and power added efficiency versus input power of a 1.5 W class-B MMIC amplifier.

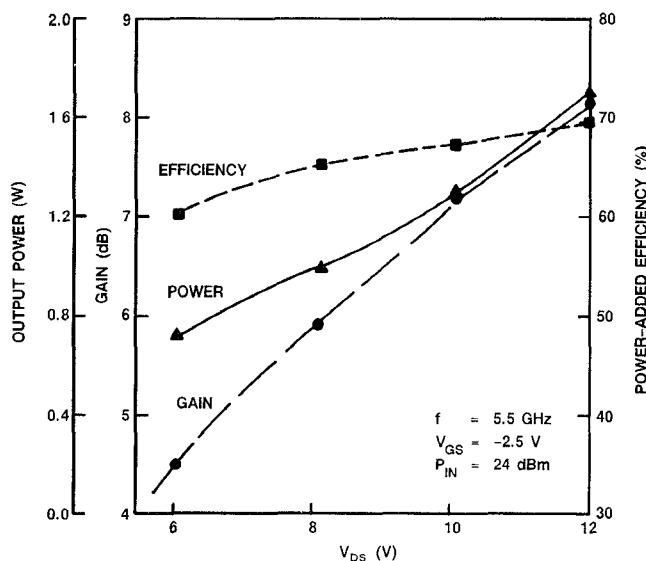

Fig. 8. Power output, gain, and efficiency versus drain-source voltage

approximately 23 V. At half  $I_{DSS}$ , the dc transconductance is 40 mS (133 mS/mm).

Several 1.5 W amplifiers were assembled on  $0.5 \times 0.5$  in $^2$  Elkonite (Cu-W) carriers. Elkonite material (a standard material for MMIC packages as well as for carriers at GTC) was chosen for its good thermal conductivity and good thermal expansion match to GaAs and alumina.

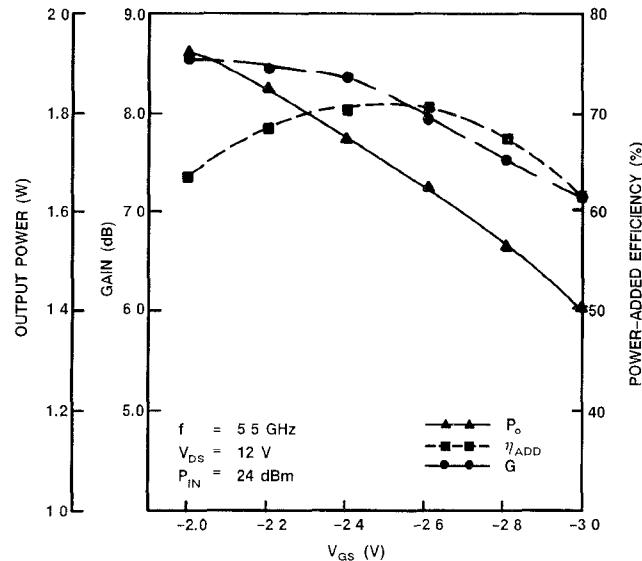

Typical measured characteristics for the IC are plotted in Fig. 7 as a function of input power at 5.5 GHz (center frequency of the 5-6 GHz design band). The amplifier has about 1.7 W power output, 8 dB gain, and 70 percent PAE. The second- and third-harmonic levels were below -26 dBc and -28 dBc, respectively. Figs. 8 and 9 depict power output, gain, and efficiency as functions of  $V_{DS}$  and  $V_{GS}$ , respectively. These plots show that GTC's class-B amplifier chips exhibit more than 60 percent PAE over a

Fig. 9. Power output, gain, and efficiency versus gate-source voltage

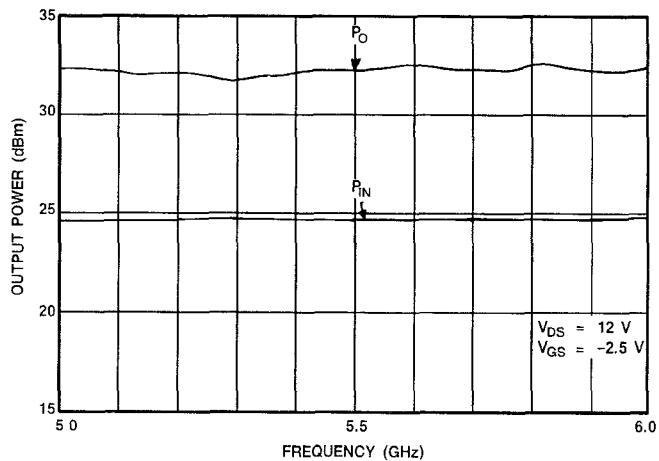

Fig. 10. Variation of power output and power input as a function of frequency over the design frequency range

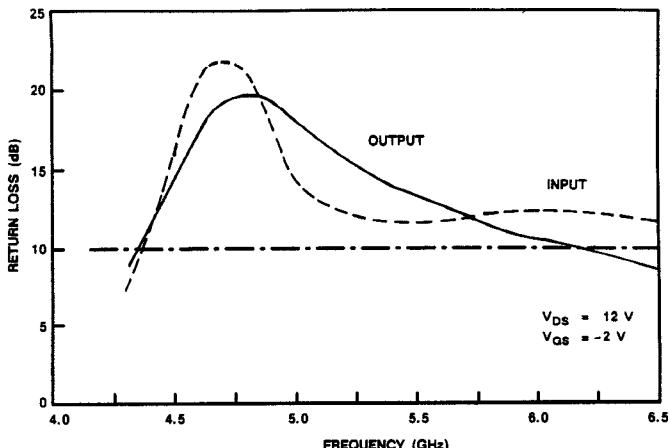

large range of bias voltages. At maximum efficiency, power output and input power as a function of frequency are shown in Fig. 10. The variations of input and output return loss are plotted in Fig. 11. Over the design band the return loss was better than 10 dB. The measured group delay of the amplifier was 0.2 ns.

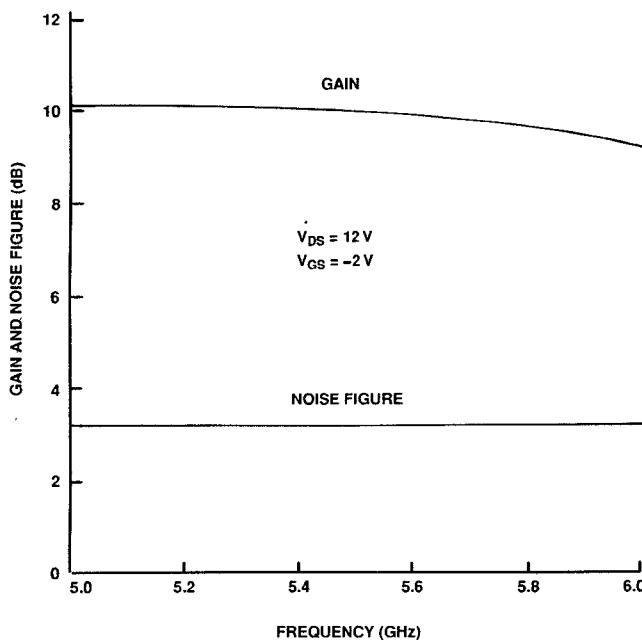

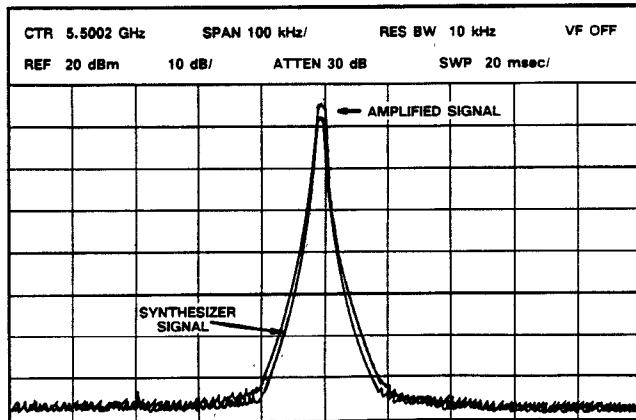

The noise figure of the class-B amplifier was measured when biased at 20 percent of  $I_{DSS}$ . Noise figure and small-signal gain as a function of frequency are plotted in Fig. 12. The noise figure was less than 3.5 dB over the 5-6 GHz band. Also, the spectrum of a frequency synthesizer signal and the amplified signal by the class-B power amplifier chip were measured and are shown in Fig. 13. It may be noted that the phase noise contribution by the amplifier is negligible. The measured AM to PM conversion was less than  $1^\circ/\text{dB}$  up to 20 dBm input power and less than  $3^\circ/\text{dB}$  up to 25 dBm input power.

Table I summarizes the measured performance versus design goals for GTC's class-B power amplifiers. At GTC we have demonstrated state-of-the-art performance for

Fig. 11. Return loss versus frequency of a 1.5 W class-B power MMIC chip.

Fig. 12. Typical small-signal gain and noise figure of a 1.5 W class-B MMIC amplifier.

Fig. 13. Spectrum of a frequency synthesizer signal and amplified signal by a class-B amplifier ( $V_{DS} = 10$  V,  $V_{GS} = -2.0$  V, attenuator value = 6 dB).

TABLE I

SUMMARY OF MEASURED RESULTS FOR CLASS B MMIC AMPLIFIERS

| Parameter                        | Goals | Measured |

|----------------------------------|-------|----------|

| Frequency (GHz)                  | 5-6   | 5-6      |

| Power Output (W), min.           | 1.5   | 1.7      |

| $P_0/\text{mm}^2$ (W/mm)         | 0.6   | 0.7      |

| Gain (dB), min.                  | 8.0   | 8.0      |

| Efficiency (%), min.             | 50    | 70       |

| VSWR, Max.                       | 2:1   | 2:1      |

| IIInd Harmonic level (dBc), max. | -20   | -26      |

| IIIRD Harmonic level (dBc), max. | -20   | -28      |

class-B power amplifier MMIC's. This excellent performance is attributed to a new IC design method, simple circuit topology, second- and third-harmonic termination at the drain location, and high-yield, high-performance MSAG processing.

## VI. CONCLUSIONS

A fully monolithic C-band class-B power amplifier with 70 percent PAE, 8 dB gain, and 1.7 W power output fabricated using the ITT MSAG process (refractory self-aligned gate technology) is demonstrated. The IC's exhibited excellent performance, including -26 and -28 dBc second- and third-harmonic levels at the maximum efficiency, clearly demonstrating the importance of careful harmonic termination.

## ACKNOWLEDGMENT

The authors gratefully acknowledge the assistance of many colleagues at ITT/GTC, including layout, fabrication, packaging, and microwave test groups.

## REFERENCES

- [1] I. J. Bahl, R. Wang, A. E. Geissberger, E. L. Griffin, and C. Andricos, "C-Band 10 watt MMIC amplifier manufactured using refractory SAG," to be presented at the 1989 IEEE Microwave and Millimeter Wave Integrated Circuit Symposium, Long Beach, CA.

- [2] F. N. Sechi, "High efficiency microwave FET power amplifiers," *Microwave J.*, vol. 24, pp. 59-66, 1981.

- [3] M. Cohn, J. E. Degenford, and R. G. Freitag, "Class-B operation of microwave FETs for array module applications," in *1982 IEEE MTT-S Int. Microwave Symp. Dig.*, pp. 169-171.

- [4] R. G. Freitag, J. E. Degenford, and M. Cohn, "High-efficiency single-ended and push-pull class-B power amplifiers," in *Proc. 1985 GOMAC Conf.* (Orlando, FL), pp. 159-162.

- [5] J. R. Lane, R. G. Freitag, H.-K. Hahn, J. E. Degenford, and M. Cohn, "High-efficiency 1-, 2-, and 4-W class-B FET power amplifiers," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-34, pp. 1318-1325, Dec. 1986.

- [6] S. Nishiki and T. Nojima, "Harmonic reaction amplifier—A novel high-efficiency and high-power microwave amplifier," in *1987 IEEE MTT-S Int. Microwave Symp. Dig.*, pp. 963-966.

- [7] T. Nojima and S. Nishiki, "High-efficiency microwave harmonic reaction amplifier," in *1988 IEEE MTT-S Int. Microwave Symp. Dig.*, pp. 1007-1010.

- [8] B. Kopp and D. D. Heston, "High-efficiency 5-W power amplifier with harmonic tuning," in *1988 IEEE MTT-S Int. Microwave Symp. Dig.*, pp. 839-842.

- [9] M. Avasala, D. S. Day, S. Chan, P. Gregory and J. R. Basset, "High-efficiency small size 6 W class AB X-band amplifier module

using a novel MBE GaAs FET," in *1988 IEEE MTT-S Int. Microwave Symp. Dig.*, pp. 843-846.

[10] B. D. Geller and P. E. Goettle, "Quasi-monolithic 4-GHz power amplifiers with 65-percent power-added efficiency," in *1988 IEEE MTT-S Int. Microwave Symp. Dig.*, pp. 835-836.

[11] D. M. Snider, "A theoretical analysis and experimental confirmation of the optimally loaded and overdriven RF power amplifier," *IEEE Trans. Electron Devices*, vol. ED-14, pp. 851-857, Dec. 1967.

[12] A. E. Geissberger, I. J. Bahl, E. L. Griffin and R. A. Sadler, "A new refractory self-aligned gate technology for GaAs microwave power FET's and MMIC's," *IEEE Trans. Electron Devices*, vol. 35, pp. 615-622, May 1988.

†

**Inder J. Bahl** (M'80-SM'80-F'89) was born in India in 1944. He received the M.S. degree in physics and the M.S. degree in electronics engineering from Birla Institute of Technology and Science, Pilani, India, in 1967 and 1969, respectively. In 1975, he received the Ph.D. degree in electrical engineering from Indian Institute of Technology (IIT), Kanpur, India.

From 1969 to 1974, he was a Senior Research Assistant at IIT Kanpur. During the years 1974-1978, he was with the Advanced Centre for Electronic Systems as a Research Engineer, where he was engaged in research on p-i-n diode phase shifters, microwave integrated circuits, and printed antennas. From 1979 to 1981, he was a Research Associate at the University of Ottawa, Ottawa, Canada. Prior to joining ITT in 1981, he spent five months at the Defence Research Establishment, Ottawa, Canada, working on millimeter-wave systems as a Research Scientist. At ITT GTC, in his present capacity as a Technical Staff Fellow and Department Head, he is responsible for the design and test development of GaAs analog IC's.

Dr. Bahl is the author or coauthor of over 100 research papers. He has authored or coauthored four books: *Microstrip Lines and Slotlines* (Artech House), *Microstrip Antennas* (Artech House), *Millimeter Wave Engineering and Applications* (John Wiley), and *Microwave Solid State Circuit Design* (John Wiley). He holds five patents in the areas of microstrip antennas and microwave circuits.

†

**Edward L. Griffin** (M'76) was born in Philadelphia, PA, in 1947. He obtained the B.S. degree in engineering physics in 1969, the M.S. degree in physics in 1971, and the Ph.D. degree in solid-state physics in 1975, all from the University of Illinois. In 1988, he was awarded an M.B.A. from Duke University.

He joined the ITT Gallium Arsenide Technology Center in February 1982. Prior to joining ITT, he worked for seven years at Hughes Aircraft Space and Communications Group on the development of a variety of active and passive microwave components for satellite applications. Areas in which he concentrated included microwave filters, CAD and numerical analysis, design manufacturing of low noise and power GaAs FET hybrid amplifiers, and reliability testing. Prior to becoming Director of Engineering, he served as Manager of the GTC MMIC Design and Test Department for three years, followed by two years as Manager of the GaAs IC Fabrication Department. As Director of Engineering at GTC, he has been involved with all aspects of GaAs IC design with all packaging, and testing. He became Director of Engineering/Operations in 1988.

Dr. Griffin served on the IEEE MTT-S Microwave Filter Steering Committee from 1981 to 1983 and the IEEE MTT-S Low-Noise Techniques Technical Committee in 1985. He is the author or coauthor of more than 15 technical papers and is the coholder of six microwave patents. Dr. Griffin is a member of the American Physical Society.

†

**Arthur E. Geissberger** (M'84) received the B.S. degree in physics from Lafayette College, Easton, PA, in 1975 and the M.S. and Ph.D. degrees in solid-state physics from Brown University, Providence, RI, in 1976 and 1981, respectively.

From 1981 to 1983, he was a member of the opto-electronics group at the Xerox Corporation, Palo Alto Research Center, Palo Alto, CA. There he was responsible for fabrication and structural investigation using Raman spectroscopy of bulk and thin-film oxide glasses. He joined the ITT-Gallium Arsenide Technology Center, Roanoke, VA, in August 1983. In his current position, he is responsible for advanced device and process development in the area of microwave and digital self-aligned gate GaAs integrated circuits.

†

**Constantine Andricos** was born in New York City in 1934. He attended Columbia University, New York, NY, from which he received the R.S.E.E. degree in 1956 and the M.S.E.E. degree in 1958.

In 1976, he joined ITT Gilfillan and was responsible for the development of receivers and synthesizers for radars. He has been active in GaAs MMIC development for ten years and has designed components for T/R modules including low-noise amplifiers, programmable phase shifters and attenuators, power amplifiers, and switches. He is presently Manager of GaAs Microwave Development for phased array radars at Gilfillan, Van Nuys, CA.

†

**Thomas F. Brukiewa** (S'64-M'75), of Los Angeles, CA, formerly from Maryland, is a Senior Engineering Manager at ITT Gilfillan, Van Nuys, CA. He received the B.S. (1964) and an M.S. (1967) degrees in electrical engineering from Drexel University, Philadelphia, PA.

He joined Hughes Aircraft in 1967, where he was in charge of signal processing and tracking within the Advanced Programs Division. He then became an Associate Manager of the Sensor System Development Department within the F-14 program, which provided the radar hardware and software functional and system design and analysis. Mr. Brukiewa joined ITT Gilfillan in August 1983 and became the Program Manager for the Hybrid Bistatic Radar Manager for Advanced Systems. Since early 1987, he has been the manager of all active array radar programs within ITT Gilfillan, as well as Passive Radar Manager for Advanced Systems. These include the MMIC, power conditioning, variable power T/R module, and in-house IR&D efforts.